Optimizing board designs with multipack devices

Richard Lin (Ducky) ducky edg edg-model multipack

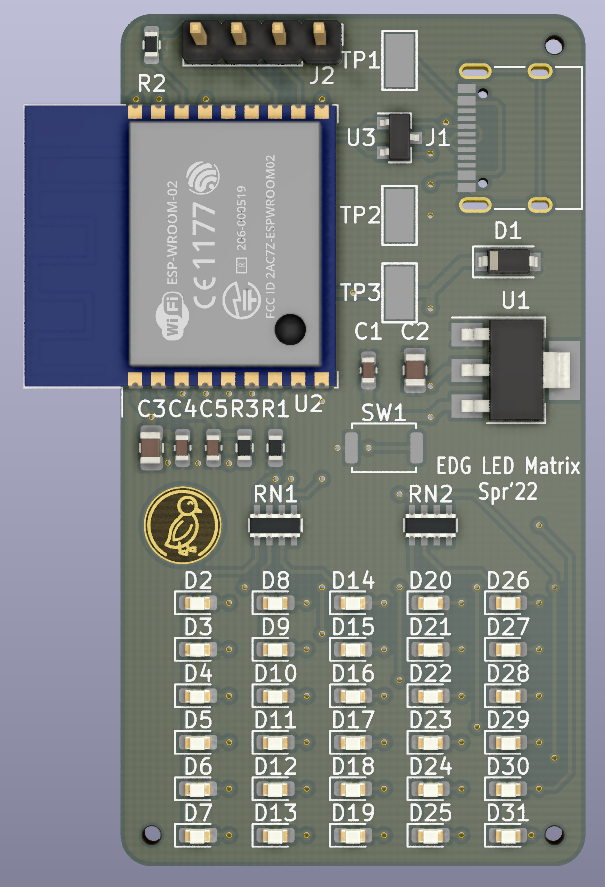

Can you spot the difference from last week's board design (I mean, aside from the duck 🦆 moving)? Right above the LEDs, instead of 4 resistors, there's now 2 4-pack resistors (RN1 and RN2).

Up to this point, the board design HDL followed a pretty strict hierarchy block design structure. Hierarchical design is a good way to encapsulate knowledge - for example, I can ask for an indicator LED circuit, and the system can provide the implementation (a LED + resistor - with resistance automatically determined), and this can happen recursively (the resistor can then be automatically selected from a parts table). However, in practical electronics (and probably also other fields), this only works as a first-order approximation - a strict hierarchy can hamper design. In this example, instead of a bunch of individual resistors that take up a lot of board area, we can instead consolidate them into a resistor array that's much smaller - potentially saving on board area, parts count, and cost.

More details on the pull request - including examples of how the user-facing HDL looks. This feature also came together surprisingly fast (though pretty front-loaded with a lot of design effort), much more so than array ports which had a troubled multi-month development cycle. Though to be fair, that was also a much more complex feature.