Weekly WIPs (work in progress) are shorter posts that describe projects or features that are still being worked on, as opposed to fuller posts looking at completed work. Most features take weeks to build, so these are smaller intermediate progress reports, but hopefully will still be interesting!

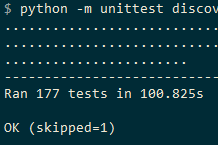

While red tests (as in the last update) are a normal part of the development cycle, it's even nicer to see tests go fully green.

While the last update (linked above) discussed the beginnings and motivation of block-side port arrays, this week was focused on building out an end-to-end slice of the feature, namely support for block-side port arrays and generators, but excluding array-to-array connections. And as might be expected, there's quite a bit of plumbing needed to get this feature end-to-end, from the frontend HDL changes last week, to all the model changes needed to support that (for example, suggested-name for allocating ports and a way to get elements of a port for generators) and the compiler improvements needed (namely, allocation resolution logic, which resulted in yet another refactoring to make IsConnected and arrays play nicely).

But, as seen below, things are working. The infrastructure for generators and port arrays is there and the current tests are passing. Next step is to create a base microcontroller class, refactor the existing microcontrollers to use it, and then move on to array-array connections.